Silicon低抖動(dòng)晶體振蕩器適用于FPGA的參考時(shí)鐘源

來(lái)源:http://m.eitherspanlaw.com 作者:億金電子 2019年11月12

Silicon低抖動(dòng)晶體振蕩器適用于FPGA的參考時(shí)鐘源

1.簡(jiǎn)介

受市場(chǎng)對(duì)不斷增長(zhǎng)的網(wǎng)絡(luò)帶寬需求的推動(dòng),高速數(shù)字通信設(shè)備制造商期望通信半導(dǎo)體供應(yīng)商提供最新的基于高速標(biāo)準(zhǔn)的數(shù)字通信協(xié)議構(gòu)建塊.FPGA供應(yīng)商已經(jīng)接受挑戰(zhàn)并生產(chǎn)了專(zhuān)門(mén)針對(duì)高速串行數(shù)字技術(shù)各個(gè)細(xì)分市場(chǎng)的產(chǎn)品通訊設(shè)計(jì).結(jié)果,通信和嵌入式計(jì)算產(chǎn)品設(shè)計(jì)越來(lái)越多將FPGA與嵌入式串行器/解串器(SerDes),低抖動(dòng)石英晶體振蕩器結(jié)合使用,以實(shí)現(xiàn)關(guān)鍵的高速收發(fā)器和串行協(xié)議處理.

在高速串行數(shù)字通信中,控制,減少和保持低電平信號(hào)路徑抖動(dòng)是最重要的考慮因素,尤其是當(dāng)比特率增加到數(shù)千兆比特甚至更高的范圍時(shí).FPGA供應(yīng)商和系統(tǒng)設(shè)計(jì)人員越來(lái)越意識(shí)到低抖動(dòng)數(shù)字通信絕對(duì)需要低或超低抖動(dòng)晶體振蕩器,有源晶振.Silicon Labs時(shí)序解決方案可以輕松滿(mǎn)足低抖動(dòng)時(shí)鐘要求高速串行數(shù)字通信的要求.

2. FPGA對(duì)于晶體振蕩器抖動(dòng)要求

FPGA的絕大部分市場(chǎng)份額分配給Xilinx和Altera這兩家公司.這兩個(gè)公司擁有專(zhuān)門(mén)針對(duì)各種高速串行數(shù)字通信市場(chǎng)的FPGA產(chǎn)品段.出于對(duì)市場(chǎng)的關(guān)注,這些FPGA公司已經(jīng)發(fā)布了輸入規(guī)范參考時(shí)鐘抖動(dòng)要求,可使其基于FPGA的產(chǎn)品實(shí)現(xiàn)符合規(guī)范的串行數(shù)字通信協(xié)議.盡管可以以不同的形式指定時(shí)鐘晶體振蕩器抖動(dòng),但幾乎被普遍接受高速串行數(shù)字通信鏈路的格式是頻率中的相位噪聲(抖動(dòng))掩碼的格式域.

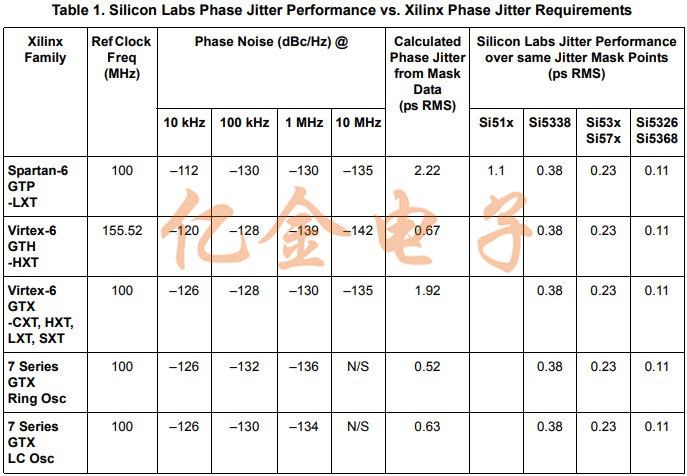

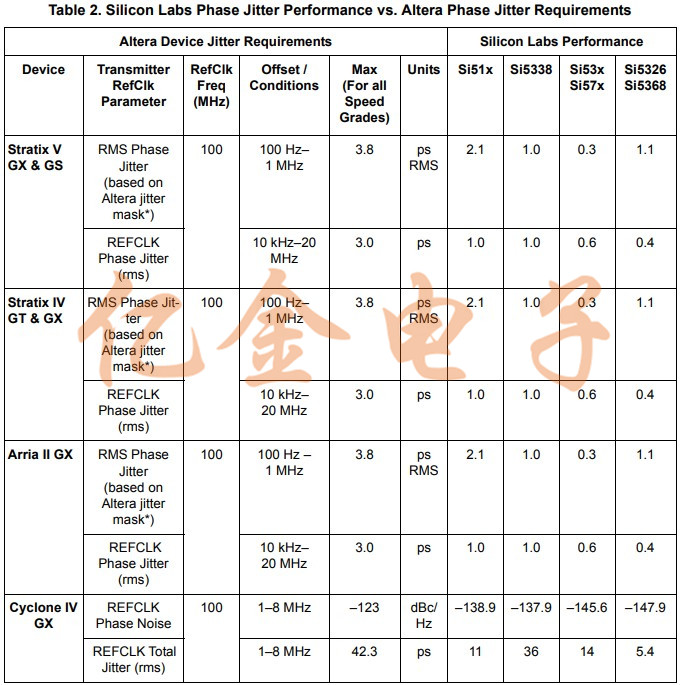

表1和表2提供了輸入兩個(gè)主要的FPGA供應(yīng)商針對(duì)目標(biāo)用于FPGA的FPGA產(chǎn)品發(fā)布的參考時(shí)鐘抖動(dòng)規(guī)范高速串行數(shù)字通信.除了這些抖動(dòng)要求外,表1和表2還提供了一些Silicon晶振,Silicon晶體振蕩器設(shè)備的抖動(dòng)規(guī)范.所選設(shè)備包括Si51x 0.1–250MHz可編程XO振蕩器,Si53x/Si570 10-1417MHz可編程XO,Si5338任意頻率,任意輸出時(shí)鐘發(fā)生器和Si5326/68任意頻率抖動(dòng)衰減時(shí)鐘.如下表所示,指定的Silicon Labs計(jì)時(shí)設(shè)備可以輕松滿(mǎn)足或超過(guò)FPGA的輸入?yún)⒖紩r(shí)鐘抖動(dòng)要求具有很大的余量,非常適合用于高速數(shù)字串行通信應(yīng)用.

.jpg) Silicon低抖動(dòng)晶體振蕩器適用于FPGA的參考時(shí)鐘源.Silicon Labs時(shí)鐘晶體振蕩器非常適合用作帶有嵌入式SerDes的FPGA的參考時(shí)鐘源,高速串行數(shù)字通信應(yīng)用.具有其他內(nèi)置功能,例如任何頻率具有0ppm的頻率誤差,出色的PSRR和具有數(shù)字可編程環(huán)路的抖動(dòng)衰減的靈活性與簡(jiǎn)單的PLL時(shí)鐘解決方案相比,Silicon Labs晶振,有源晶體振蕩器,XO振蕩器具有更高的帶寬優(yōu)勢(shì),可提供真正的系統(tǒng)優(yōu)勢(shì).

Silicon低抖動(dòng)晶體振蕩器適用于FPGA的參考時(shí)鐘源.Silicon Labs時(shí)鐘晶體振蕩器非常適合用作帶有嵌入式SerDes的FPGA的參考時(shí)鐘源,高速串行數(shù)字通信應(yīng)用.具有其他內(nèi)置功能,例如任何頻率具有0ppm的頻率誤差,出色的PSRR和具有數(shù)字可編程環(huán)路的抖動(dòng)衰減的靈活性與簡(jiǎn)單的PLL時(shí)鐘解決方案相比,Silicon Labs晶振,有源晶體振蕩器,XO振蕩器具有更高的帶寬優(yōu)勢(shì),可提供真正的系統(tǒng)優(yōu)勢(shì).

1.簡(jiǎn)介

受市場(chǎng)對(duì)不斷增長(zhǎng)的網(wǎng)絡(luò)帶寬需求的推動(dòng),高速數(shù)字通信設(shè)備制造商期望通信半導(dǎo)體供應(yīng)商提供最新的基于高速標(biāo)準(zhǔn)的數(shù)字通信協(xié)議構(gòu)建塊.FPGA供應(yīng)商已經(jīng)接受挑戰(zhàn)并生產(chǎn)了專(zhuān)門(mén)針對(duì)高速串行數(shù)字技術(shù)各個(gè)細(xì)分市場(chǎng)的產(chǎn)品通訊設(shè)計(jì).結(jié)果,通信和嵌入式計(jì)算產(chǎn)品設(shè)計(jì)越來(lái)越多將FPGA與嵌入式串行器/解串器(SerDes),低抖動(dòng)石英晶體振蕩器結(jié)合使用,以實(shí)現(xiàn)關(guān)鍵的高速收發(fā)器和串行協(xié)議處理.

在高速串行數(shù)字通信中,控制,減少和保持低電平信號(hào)路徑抖動(dòng)是最重要的考慮因素,尤其是當(dāng)比特率增加到數(shù)千兆比特甚至更高的范圍時(shí).FPGA供應(yīng)商和系統(tǒng)設(shè)計(jì)人員越來(lái)越意識(shí)到低抖動(dòng)數(shù)字通信絕對(duì)需要低或超低抖動(dòng)晶體振蕩器,有源晶振.Silicon Labs時(shí)序解決方案可以輕松滿(mǎn)足低抖動(dòng)時(shí)鐘要求高速串行數(shù)字通信的要求.

2. FPGA對(duì)于晶體振蕩器抖動(dòng)要求

FPGA的絕大部分市場(chǎng)份額分配給Xilinx和Altera這兩家公司.這兩個(gè)公司擁有專(zhuān)門(mén)針對(duì)各種高速串行數(shù)字通信市場(chǎng)的FPGA產(chǎn)品段.出于對(duì)市場(chǎng)的關(guān)注,這些FPGA公司已經(jīng)發(fā)布了輸入規(guī)范參考時(shí)鐘抖動(dòng)要求,可使其基于FPGA的產(chǎn)品實(shí)現(xiàn)符合規(guī)范的串行數(shù)字通信協(xié)議.盡管可以以不同的形式指定時(shí)鐘晶體振蕩器抖動(dòng),但幾乎被普遍接受高速串行數(shù)字通信鏈路的格式是頻率中的相位噪聲(抖動(dòng))掩碼的格式域.

表1和表2提供了輸入兩個(gè)主要的FPGA供應(yīng)商針對(duì)目標(biāo)用于FPGA的FPGA產(chǎn)品發(fā)布的參考時(shí)鐘抖動(dòng)規(guī)范高速串行數(shù)字通信.除了這些抖動(dòng)要求外,表1和表2還提供了一些Silicon晶振,Silicon晶體振蕩器設(shè)備的抖動(dòng)規(guī)范.所選設(shè)備包括Si51x 0.1–250MHz可編程XO振蕩器,Si53x/Si570 10-1417MHz可編程XO,Si5338任意頻率,任意輸出時(shí)鐘發(fā)生器和Si5326/68任意頻率抖動(dòng)衰減時(shí)鐘.如下表所示,指定的Silicon Labs計(jì)時(shí)設(shè)備可以輕松滿(mǎn)足或超過(guò)FPGA的輸入?yún)⒖紩r(shí)鐘抖動(dòng)要求具有很大的余量,非常適合用于高速數(shù)字串行通信應(yīng)用.

表1. Silicon Labs的相位抖動(dòng)性能與Xilinx的相位抖動(dòng)要求

表2. Silicon Labs的相位抖動(dòng)性能與Altera的相位抖動(dòng)要求

表3. Altera抖動(dòng)屏蔽(100 MHz RefClk)

表2. Silicon Labs的相位抖動(dòng)性能與Altera的相位抖動(dòng)要求

表3. Altera抖動(dòng)屏蔽(100 MHz RefClk)

.jpg)

正在載入評(píng)論數(shù)據(jù)...

此文關(guān)鍵字: Silicon晶振Silicon晶體振蕩器

相關(guān)資訊

- [2023-06-26]Rakon推出RakonXpress品牌的現(xiàn)成頻率...

- [2023-06-20]Cardinal晶振公司環(huán)境政策,CSM1Z-A0B...

- [2023-06-20]Cardinal晶振ROSH證明,CX532Z-A2B3C5...

- [2023-06-17]為什么選擇ClearClock有源晶振,AK2AD...

- [2021-01-21]低功耗性能且含數(shù)字溫度補(bǔ)償?shù)臅r(shí)鐘IC...

- [2020-12-04]TXC晶振車(chē)規(guī)級(jí)頻率組件最新產(chǎn)品應(yīng)用方...

- [2020-10-19]石英振蕩器系列六——產(chǎn)品未來(lái)應(yīng)用市...

- [2020-10-16]石英振蕩器系列五之如何獲取更優(yōu)良的...

銷(xiāo)售代表

銷(xiāo)售代表

.jpg)